이번 포스트에서는 회로 설계 부분에서 기초 중 기초인 풀업 , 풀다운 저항에 대해 그 동안 공부한 내용들을 참고하여 정리하고 한다.

틀린 부분이 있으면 언제든지 댓글 남겨 주세요.

풀업, 풀다운 저항이란?

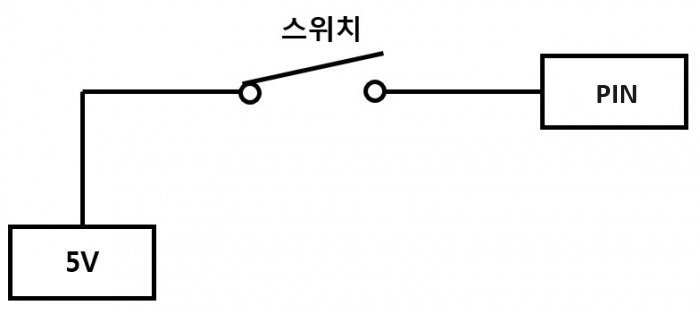

Pull Up : 어떤 핀 또는 노드의 전압을 전원(Vcc, Vdd)로 주면 전압이 높은 곳으로 끌어 올려지는 것

Pull Down : 어떤 핀 또는 노드의 전압을 접지(GND)로 주면 전압이 낮 곳으로 끌어 내려지 것

Pull Up 저항 : Pull Up이 되는 전원에 연결한 저항

Pull Down 저항 : Pull Down이 되는 접지에 연결한 저항

사용 목적?

-> 특정 핀 또는 노드의 플로팅 상태를 방지

플로팅 현상이란?

-> 0(LOW)도 아니고 1(HIGH)도 아닌 중간에 값이 0도 아니고 1도 아닌 상태

사용 용도

① Output Driver : 일반적으로 입력쪽으로 Pull up & Pull Down 저항을 사용하여 초기값을 설정하는데 사용

Output Pin은 일반적으로 0과 1을 출력하는 pin으로 적은 전류만 인가할수 있다.

따라서 많은 전류를 필요로 하는 부하(회로 및 부품)가 있을 경우 정상적으로 동작 시킬수 없다.

이 경우 Pull Up 저항을 사용한다.

Pull Up / Down 저항 값 선택시 고려 사항

1. 누설 전류

2. 풀업(풀다운)저항과 부하단 저항과의 전압분배

3. 커패시터 충방전 속도 ( T = RC)

'HW > 일반 회로 이론' 카테고리의 다른 글

| 풀업 / 풀다운 저항 추가 심화 ① (0) | 2025.03.25 |

|---|---|

| 플로팅 상태 와 하이임피던스(High-Z) (0) | 2024.12.06 |

| Push Pull & Open drain (0) | 2024.07.09 |

| C 소자 특성 (0) | 2024.06.26 |

| L 소자 특성 (0) | 2024.06.23 |