※ 해당 글은 개인 공부 기록을 남겨놓는 것이 목적임으로 오류가 발생할수 있습니다.

오류 또는 업데이트된 사항이 있다면 댓글로 알려주시면 감사하겠습니다.

아래 글은 STM32F429ZI datasheet와 Reference manual를 기준으로 작성되었습니다.

RCC(Reset Clock Controller)는 STM32의 Reset과 Clock을 관장하는 장치이다.

RCC는 두 부분으로 나뉜다,

1.RTCCLK

2.SYSCLK : WATCHDOG 공급되는 2차 클럭과 GPIO, USART, TIM 등과 관련된 HCLK, PCLK , AHA, AHB에

공급되는 시스템 클럭

1) SYSCLK은 아래와 같이 대부분 HSI, HSE 사용한다.

HSI(High Speed Internal) clock

HSE(High Speed External) clock

HSI와 HSE는 PLL 또는 Prescaler를 통해 원하는 주파수로 변경 후 SYSTEM CLOCK(SYSCLK)으로 사용 한다.

SYSCLK 값을 이용하여 FCLK, HCLK, PCLK 값을 구할 수 있다.

- FCLK : CPU에서 사용되는 Clcok

- HCLK : AHB 버스에 사용되는 Clock으로 memory controller, interrrupt controller에 사용

- PCLK : APB 버스에 사용되는 Clock으로 GPIO, UART, SPI 등에 사용된다.

2) SYSCLK가 아니라 부가 목적으로 사용되는 LSI, LSE clock이 있다. 일반적으로 RTC와 watchdog용도로 쓰인다.

LSI(Low Speed Internal) RC clock

LSE(Low Speed External) crystal clock

3) 주요 내부 버스

AHB( Advanced High Performance Bus ) - DMA, RCC, Flash Memory I/F, OTG 등이 연결됨. 사용 클럭 HCLK

APB2( Advanced Peripheral Bus 2 ) - UART1, ADC, TIM1, SPI1, GPIO, AFIO 등이 연결됨. 공급 클럭 PCLK

APB1( Advanced Peripheral Bus 1 ) - UART2, 3, TIM2, 3, 4, I2C, SPI2, 3 등이 연결됨. 공급 클럭 PCLK1

여기서는 RCC 레지스터 중 RCC_CFGR와 RCC_CR 레지스터를 다룰 것이다.

부가적으로 RCC_PLLCFGR , RCC_CIR , RCC_APB1RSTR, RCC_APB1ENR, RCC_AHB1LPENR, RCC_BDCR, RCC_CSR, RCC_SSCGR, RCC_PLLI2SCFGR 등 더 많은 레지스터들이 존재한다. 추가적으로 궁금하다면

레퍼런스를 참고 바란다.

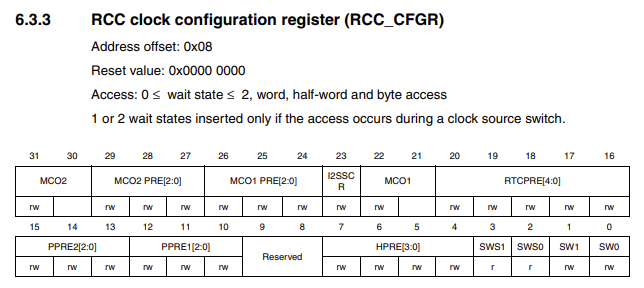

1. RCC_CFGR 레지스터(RCC clock configuration register)

: 해당 레지스터를 어떻게 설정하느냐에 따라 어떤 클럭을 쓰고, 클럭 주파수와 분주비를 결정할수 있다.

| 비트 이름(위치) | 설명 | 비트 설정 |

| MCO2[31:30] | Microcontroller clock output 2 | 00: System clock (SYSCLK) selected 01: PLLI2S clock selected 10: HSE oscillator clock selected 11: PLL clock selected |

| MCO2 PRE[29:27] | MCO2 prescaler | 0xx: no division 100: division by 2 101: division by 3 110: division by 4 111: division by 5 |

| MCO1 PRE[26:24] | MCO1 prescaler | 0xx: no division 100: division by 2 101: division by 3 110: division by 4 111: division by 5 |

| I2SSR[23] | I2S clock selection | 0: PLLI2S clock used as I2S clock source 1: External clock mapped on the I2S_CKIN pin used as I2S clock source |

| MCO[22:21] | Microcontroller clock output 1 | 00: HSI clock selected 01: LSE oscillator selected 10: HSE oscillator clock selected 11: PLL clock selected |

| RTCPRE[20:16] | HSE division factor for RTC clock | 00000: no clock 00001: no clock 00010: HSE/2 00011: HSE/3 00100: HSE/4 11110: HSE/30 11111: HSE/31 |

| PPRE2[15:13] | APB high-speed prescaler (APB2) | 0xx: AHB clock not divided 100: AHB clock divided by 2 101: AHB clock divided by 4 110: AHB clock divided by 8 111: AHB clock divided by 1 |

| PPRE1[12:11] | APB Low speed prescaler (APB1) | 0xx: AHB clock not divided 100: AHB clock divided by 2 101: AHB clock divided by 4 110: AHB clock divided by 8 111: AHB clock divided by 16 |

| HPRE[7:4] | AHB prescaler | 0xxx: system clock not divided 1000: system clock divided by 2 1001: system clock divided by 4 1010: system clock divided by 8 1011: system clock divided by 16 1100: system clock divided by 64 1101: system clock divided by 128 1110: system clock divided by 256 1111: system clock divided by 512 |

| SWS[3:2] | System clock switch status | 00: HSI oscillator used as the system clock 01: HSE oscillator used as the system clock 10: PLL used as the system clock 11: not applicable |

| SW[1:0] | System clock switch | 00: HSI oscillator used as the system clock 01: HSE oscillator used as the system clock 10: PLL used as the system clock 11: not applicable |

1) 내부 클럭 / 외부 클럭 선택

STM32는 클럭이 내부(HSI)/외부(HSE)로 나누어 진다. SYSCLK는 프로그래머가 어떻게 설정하느냐에 따라 3가지에

하드웨어적으로 자동 연결된다.

| 클럭 | 클럭 주파수 | 설명 |

| HSI | 16 MHZ | 내부 RC 클 |

| HSE | 4 ~ 26MHZ | 외부 오실레이터 클 |

| PLLCLK | ~ 180MHZ | 프로그래머가 HSE 또는 HSI 둘 중 하나를 선택하여 파생된 클럭 |

2) SW 비트를 통해 SYSCLK 소스를 어떤 것을 사용할지 설정한다.

일반적으로 PLLCLK을 사용하므로 RCC_CFGR 레지스터의 SW 비트는 '10'으로 설정한다.

3) AHB에 입력되는 클럭 분주는 1/1로 설정한다고 가정 시 , RCC_CFGR 레지스터의 HPRE 비트를 '0000'으로 설정한다.

4) APB1에 입력되는 클럭 분주는 1/2로 설정한다고 가정 시 , RCC_CFGR 레지스터의 PPRE1 비트를 '100'으로 설정한다.

5) APB2에 입력되는 클럭 분주는 1/1로 설정 가정 시, RCC_CFGR 레지스터의 PPRE2 비트를 '000'으로 설정한다.

2. RCC_CR(RCC_Clock_control_register) : 클럭 온 오프 제어 레지스터

: 해당 레지스터를 제어함으로써

HSI와 HSE (0 bit - HSI) / (16 bits - HSE) 하고 enable 된 HSE 또는 HSI가 준비 될 때까지 기다리게 설정할수 있다.

또한 HSI 또는 HSE가 활성화 되면 PLL를 Enable 시킨 후, 준비가 될 때까지 기다리게 설정할수 있다.